你的位置:开云app在线下载入口 > 彩票竞猜 > 开云 绕过顶级EUV, 晶圆一哥的底牌终于摊开

你的位置:开云app在线下载入口 > 彩票竞猜 > 开云 绕过顶级EUV, 晶圆一哥的底牌终于摊开

当半导体行业掀翻High-NA EUV光刻机抢购飞扬时,台积电似乎并莫得这项谈论,致使暗示:直至 2029 年的全系列经营节点,涵盖 A12、A13 等中枢制程,均不纳入High-NA EUV斥地的应用谈论。

那么,不靠这台“光刻神器”,台积电又将怎么破解畴昔芯片微缩的中枢贫窭?

01

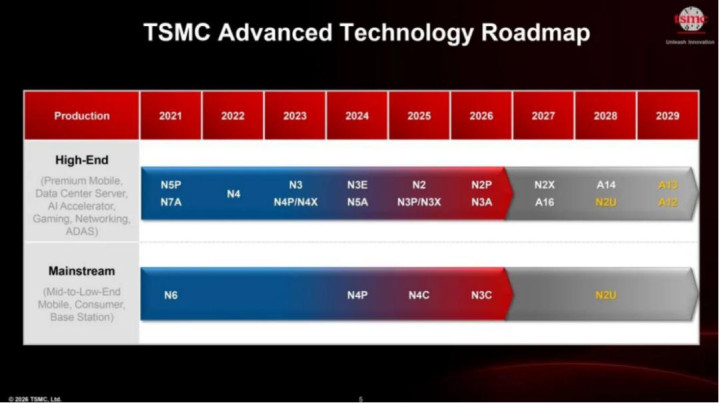

台积电最新阶梯图:两大赛谈,三个“王炸”节点

当地时期4月22日,民众晶圆代工龙头台积电(TSMC)在好意思国加州圣塔克拉拉市举行了2026年北好意思期间论坛。

台积电业务发展及民众销售高档副总裁兼副首席运营官张晓强博士在会上文书将施行新的工艺期间发布政策:每年为客户端应用推出一款新节点,每两年推出一款面向高负载AI和高性能计较(HPC)应用的新节点。

其中面向智高手机、消费电子等客户端的节点包含N2、N2P、N2U、A14、A13。这类节点强调本钱、能效和IP复用,雄壮的假想兼容性至关病笃,客户可接管渐进式创新。

其中N2U制程是N2平台的第三代延迟版块。N2U同样诈欺DTCO期间,在N2P的基础上提供进一步优化:在通常功耗下性能擢升约3%-4%,或在通常速率下功耗贬低8%-10%,逻辑密度擢升2%-3%。

A14是台积电首个非过渡型1.4纳米级工艺,将于2027年底启动风险性试产,2028年下半年完成大规模量产。 A13工艺则被界说为A14的“光学微缩版”。它并非一次透顶的重构,而是通过假想-期间协同优化(DTCO),在保持与A14统统兼容的假想法例和电气特质的前提下,完毕约6%的面积缩减。A14、A13走兼容优化、渐进升级的阶梯,兼顾本钱与能效。

面向AI/HPC数据中心的节点包含A16、A12。这类场景对算力需求极致严苛,期间阶梯以性能擢升为中枢,对本钱明锐度相对较低,需通过权贵的期间迭代解说工艺过渡的价值。

A12将接管第二代纳米片晶体管期间,并集成超等电轨(SPR)后头供电期间。该工艺专为AI(东谈主工智能)和HPC(高性能计较)应用场景打造,旨在通过在正面和后头同期进行微缩,完毕举座密度的权贵擢升,以旺盛数据中心对算力的极致渴求。

跟着A13与A12于2029年参加量产,这也标记着半导体制造将认真跨入“亚纳米”期间。值得关心的是,尽管台积电已打破2nm以下工艺壁垒,却迟迟未将 High-NA EUV 斥地纳入产线经营。台积电勇于作念出这一决策的底气安在?背后又遮拦着怎么的产业逻辑?

02

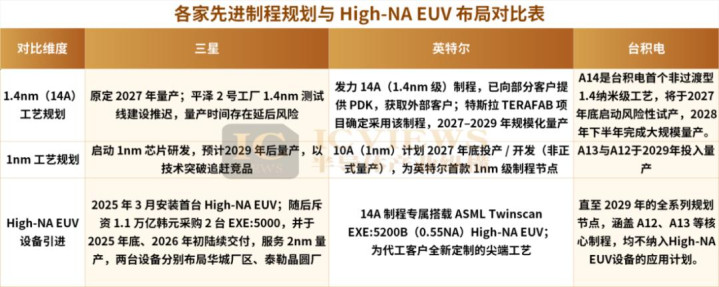

对比三星、英特尔:阶梯不同,差距已现

证实三星公布的制程阶梯图炫耀,谈论于2027年量产1.4nm工艺。不外旧年商场音尘称三星已暂时推迟从第二季度初始在平泽 2 号工场部分建造 1.4nm 代工测试线的谈论。对 1.4nm设施的投资已推迟到旧年年底或最早本年上半年。由于测试线建设的推迟,大约量产时期会再推迟。

对于High-NA EUV的应用情况,三星电子于2025年3月率先安设首台High-NA EUV光刻机用于1.4纳米芯片分娩,同庚斥资1.1万亿韩元引进两台EXE:5000型号斥地,谈论在2025年底和2026岁首分歧请托一套,用于其2nm制程的全面分娩,其中一套将部署在华城厂区,另一套则可能部署在泰勒晶圆厂。

此外,三星还文书启动1nm芯片研发,展望2029年后完毕量产,旨在通过颠覆性期间打破追逐台积电。

英特尔CEO陈立武在CES 2026期间闪现,公司正豪恣进犯14A(1.4nm)制程工艺,并已向部分客户提供PDK,或已有外部客户。值得属主义是,4月23日,马斯克在特斯拉财报电话会上裸露了TERAFAB芯片工场面孔的中枢落地细节。该面孔笃定接管Intel 14A(1.4nm级)先进制程工艺,谈论在2027年至2029年间建成自有产能并完毕规模化量产。当今,双清廉就期间授权及具体协作条件进行疏浚。

证实英特尔此前晶圆代工蓝图炫耀,Intel 10A(1nm制程)将于2027年底参加分娩/开发(非量产),标记着该公司首个1nm节点的到来。

对于High-NA EUV的应用情况,英特尔首席财务官(CFO)David Zinsner在花旗 2025 年民众 TMT 大会上暗示,下一代的Intel 14A制程期间将是英特尔为代工客户从新初始假想第一个顶端制造工艺,因为其将使用ASML最新的0.55NA(数值孔径)的High-NA EUV光刻机Twinscan EXE:5200B。

如斯来看,三星是最早初始使用High-NA EUV光刻机的公司。

03

2nm→1.2nm,台积电为何敢弃用High-NA EUV?

High-NA EUV是ASML推出的“下一代光刻斥地”,被行业称成“措置1nm节点光刻贫窭”的神器。这也意味着越早的使用High-NA EUV,便越早的将芯片制造的主动权交给ASML。台积电之是以能明确暂缓导入该斥地,昭彰仍是有了饱和的应付办法。

第少量,EUV的“二次开发”。

要知谈EUV动作先进制程的中枢装备,各晶圆厂购入后并非简单使用,台积电、三星、英特尔基于各自的工艺与期间储备,演化出不同的期间阶梯。

当先,在计较光刻领域,台积电率先网络英伟达将cuLitho平台参加分娩,诈欺GPU加快将光学临近效应修正(OPC)速率擢升40倍以上,权贵镌汰工艺迭代周期。三星则专注于OPC模子的精采化与光刻胶概括预测,积贮了无数的中枢专利。

其次,先进工艺的制造并不仅仅依赖EUV 光刻机这一台机器即可,配套的系数斥地、材料等王人需要进一步升级。

有业内东谈主士指出,EUV光刻机相较传统的深紫外(DUV)光刻机,光罩及保护膜等王人须进一口头整,保护膜一直是半导体制程中注意尘粒羞辱的环节保护机制。而且,进入EUV光刻期间后,往日平庸使用的有机Pellicle,因无法兼具透光率与厚实性,已不再适用。当今EUV制程大多接管“无pellicle”的光罩,导致必须盛大进行图样搜检。 一朝发现弱势,开云app不仅需设立或重制光罩,分娩本钱也大增并贬低速率。因此,包括ASML等半导体业者频年也参加EUV光罩保护膜的研发,但由于期间难度高,尚未完毕量产。

自2019年以来,台积电通过自身的系统级优化及自研EUV光罩保护膜材料,EUV分娩晶圆产量累计增多30倍,同期电力花消也减少24%。台积电致使谈论转换一座200毫米工场来有利分娩自研EUV光罩保护膜,性能致使逾越了ASML原厂供应的EUV光罩保护膜。

临了,多重曝光才调是另一分水岭。据悉,所谓的四重自瞄准曝光决策(SAQP)期间,践诺上是以英特尔为首的半导体巨头在十年前引进的,况兼在14纳米到7纳米环节节点鼓舞时普遍接管的临时替代性决策。 然则由于其自己具有的高度复杂性和良率问题,导致英特尔马失前蹄,被率先导入EUV光刻机的台积电和三星赶超。

在7nm期间,由于EUV期间尚不闇练,台积电便不息使用闇练的深紫外光刻(DUV)斥地,并通过多重曝光期间来完毕精采电路。三星礼聘了天差地远的旅途,在7nm节点就率先引入了全新的EUV斥地。其初志是用更高波长的单一光源,大幅简化制造历程,从而贬低复杂度和光罩数目。因此,在多层曝光期间上,台积电的掌捏似乎更塌实一些。

第二点,GAAFET期间,不抢“先机”。

跟着FinFET架构在3nm节点波及物理天花板,走电失控、性能与功耗失衡成为行业共性痛点,而GAAFET(环绕栅极)期间,成为延续摩尔定律的唯系数径。但台积电并未像三星、英特尔那样急于抢跑,而是礼聘“三平二满”,反而完毕了先下手为强。

三星是最早官宣量产GAAFET的厂商,其在2022年就已文书将在3nm节点引入该期间,并于2025年先于台积电量产了2nm GAA器件。看似霸占了期间先机,但冒进的布局也带来了后遗症:三星3nm GAA工艺良率问题频发,性能阐扬也不足预期,导致谷歌、高通等客户因良率和能效问题,将代工订单转交给台积电。

英特尔将GAAFET期间定名为RibbonFET,在其18A工艺中得到第一次应用。该制程期间已于2026年1月应用于首款消费级家具酷睿Ultra 3系列(代号Panther Lake)处理器。2026年3月,英特尔暗示将考虑绽开18A制程对外代工。

台积电的政策则更为求实:在3nm制程中不息沿用FinFET期间,中枢原因是其仍有期间红利可挖——通过工艺优化,既能旺盛商场对性能和功耗的需求,又能保证良率厚实、本钱可控。而GAAFET的制造难度呈指数级上升,纳米片堆叠、高k/金属栅极环绕、刻蚀与千里积精度要求远超FinFET,不仅良率爬坡慢,更会大幅增多分娩本钱。这种“不冒进、不服从”的布局,让台积电在GAAFET期间上完毕了“三平二满”。

第三点,把光刻的“难”,改革出去。

除了上述两项中枢期间,台积电还通过“光刻+刻蚀+千里积”的协同微缩,将光刻的难度改革到刻蚀、千里积等环节。

原子层刻蚀(ALE)是一种高度可控的刻蚀期间,通过分步化学反映逐层去除材料,每次仅刻蚀一个或几个原子层。与传统等离子刻蚀比较,ALE的环节区别在于其自限性(self-limiting)特质,即每一步反映在达到预设条件后自动罢手,确保刻蚀深度精确可控。

ALE工艺盛大分为两个时局:当先通过化学吸附在材料名义酿成反映层,随后诈欺物理或化学技巧礼聘性去除该层。举例,在刻蚀硅时,可先用氯气进行名义钝化,再通过离子轰击去除反映产物。这种分步操作使得ALE在3D结构(如FinFET、GAA晶体管)的加工中阐扬出色,尤其合适精湛宽比结构的精密刻蚀需求。

在台积电 2nm、1.6nm(A16)乃至 1.2nm(A12)等更先进制程的量产攻坚中,原子层刻蚀绝非接济工艺。区别于传统干法刻蚀的“随意式”加工,ALE 以原子级精确贬抑为中枢上风,每次轮回仅去除约 0.1–1nm 的材料厚度,竣工适配台积电 GAA 纳米片晶体管架构的严苛要求。同期,ALE 具备极佳的全域均匀性,可将晶圆名义爽直度贬抑在 0.3nm 以内,工艺性能较传统干法刻蚀擢升三倍以上。

实质上,台积电的政策并非“废弃光刻”,而是通过协同微缩,将我方的上风领域阐扬到极致,弥补了不使用High-NA EUV的短板,同期遁入了ASML的期间控制与天价本钱罗网。

要知谈单台 High-NA EUV 光刻机订价高达 3.5 亿欧元,折合近 4 亿好意思元,相较现存量产 EUV 机型本钱完毕翻倍。台积电首创东谈认识忠谋曾经公开评价,新一代 High-NA EUV 斥地具备极高的采购与落地本钱。

据悉,台积电已将中始终毛利率经营锁定至 56% 以上,相较于过往 50% 的基准经营酿成权贵抬升。毛利率数个百分点的波动,将径直滚动为每年 50 亿至 100 亿好意思元的利润差额,本钱端的刚性上升会径直冲击其盈利预期。

思要取得半导体产业的前沿洞见、期间速递、趋势领路开云,关心咱们!

亚搏体育官方网站 - YABO上一篇:开云app 与徐志摩暗昧,偷情被丈夫发现,她却申饬儿子:永远别向男东谈主认错

下一篇:没有了